vir: ComputerWorld

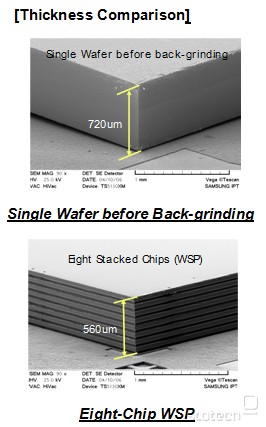

Proces proizvodnje se generično imenuje TSV in omogoča gradnjo trorazsežnih vezij, Samsung pa mu pravi wafer-level stack process (WSP). Uspeli so stlačiti osem dvogigabitnih NAND-čipov enega nad drugega v debelino le dobrega pol milimetra. Samsung pojasnjuje, da ima večja gostota nekaj prednosti, med njimi 40 odstotkov nižjo porabo energije. Trenutno predstavljeni moduli so zgrajeni iz čipov v 40 nm-tehnologiji, a že načrtujejo uporabo tudi v manjši litografiji. Na prodajnih policah nove module pričakujemo v drugi polovici prihodnjega leta, najprej predvsem za počasnejše vrste pomnilnika, saj pri tovrstni sestavi največji problem hlajenje.