vir: IEEE Spectrum

vir: IEEE Spectrum

Ob omembi 3D čipov danes nihče več ne bo posebno vznemirjen, saj jih že imamo v širši uporabi, na primer v pomnilniku flash. Napravijo jih tako, da posamezne sloje silicija zlagajo v višino in jih med seboj povežejo s kontakti (through-silicon vias ali TSVs). Grda podrobnost je, da so te vertikalne povezave posejane relativno na redko - na vsakih nekaj mikrometrov, se pravi, nekaj velikostnih razredov več od razsežnosti tranzistorjev, ki jo merimo v nanometrih. Ideal in naslednja stopnja izgradnje integriranih vezij je monolitni blok, kjer bi vsa logika stala v enem samem kosu polprevodnika, z veliko gostejšimi vertikalnimi podatkovnimi vodili. Poglavitna ovira pri razvoju takih postopkov je dejstvo, da silicijeva litografija zahteva visoke temperature, okrog tisoč stopinj Celzija, kar bi uničilo obstoječe sloje.

Pred leti je ekipa okrog Maxa Shulakerja na Univerzi Stanford začrtala zasnovo monolitnega 3D čipa, pri kateri bi sloje izmenično sestavljala računska logika s tranzistorji iz ogljikovih nanocevk in pa pomnilnik RRAM (resistive random-access memory). Oba elementa je mogoče napraviti s procesi, ki tečejo med 120 in 450 stopinjami Celzija, se pravi, pri dovolj nizki temperaturi, da izgrajevanje enega sloja ne bi poškodovalo tistih spodaj. Inženirji so tako predlani napravili "umetni nos" iz štirislojnega čipa, kar je bilo prvo delujoče monolitno tridimenzionalno integrirano vezje. Toda hkrati sta obe navedeni tehnologiji še v razvojni fazi - kljub temu, da smo se napovedi o njih že dodobra naposlušali. Prvi tranzistor iz ogljikovih nanocevk je star že 21 let, toda v uporabi jih še kar ni, ker sta proizvodnja in nameščanje nanocevk premalo zanesljivi in trpita za velikim številom defektov. Memristorje, oziroma RRAM, za katere je bilo mišljeno, da bodo spričo nevolatilnosti zamenjali pomnilnik flash, pa preprosto zavira dejstvo, da je proizvodnja obstoječega pomnilnika tako poceni in utečena, da bodo firme šle v resno menjavo tehnologije šele tedaj, ko bodo pridobitve zares občutne in RRAM stoodstotno zanesljiv.

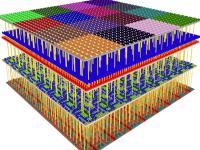

Na tem mestu se je vmešala Agencija za napredne obrambne raziskave - DARPA. Američani so lani sprožili poldrugo milijardo dolarjev težak širokopotezen program Electronics Resurgence Initiative (ERI), katerega namen je iznajti revolucionarno nove načine dizajniranja in izdelave elektronskih vezij. Program je mnogostranski, samo za vzorec pa naj omenimo, da vanj med drugim spada snovanje čipov, ki se na strojni ravni prilagajajo specifičnim aplikacijam, pa s strojnim učenjem podprto programje za dizajn čipov, ki bi majhni skupini inženirjev omogočila napraviti SoC, za katerega je trenutno potrebnih sto ljudi ... Eden od projektov v okviru ERI pa je tudi zasnova monolitnega 3D SoCja - kjer so opazili Shulakerjevo skupino in ji namenili 61 milijonov dolarjev za obdobje treh let, da zasnovo pripelje v tovarno. Shulaker, ki je s Stanforda medtem odšel na MIT, se je povezal z livarno SkyWater Technology iz Minnesote in pred dnevi na Darpini konferenci pokazal svež reženj s SkyWaterjeve proizvodne linije (na sliki). Vezje ima dva sloja: spodnjega sestavljajo tranzistorji iz nanocevk, zgornjega RRAM. Naslednja stopnja razvoja bo podvojitev slojev na štiri, nato sledi optimizacija donosa.

Važna podrobnost je, da so ti čipi napravljeni v 90-nanometrskem proizvodnem procesu, ki ga SkyWater edinega premore. Se pravi, v tehnologiji, ki je bila v industriji centralnih mikroprocesorjev aktualna pred petnajstimi leti. Toda ravno v tem je smisel Darpinih namer, saj inženirji trdijo, da lahko s tako zasnovanimi čipi konkurirajo današnjim 10-nanometrskim, kar bi starejšim livarnam, ki ne zmorejo grozljivo dragih posodobitev proizvodnje, vdihnilo novo življenje. To je seveda zelo pogumna trditev, ki jo bodo morali šele dokazati. Toda po drugi plati so ravno takšni odtrgani podvigi hvaležna tarča državnega financiranja, ker se jih bo redkokatero komercialno podjetje upalo lotiti z lastnim denarjem. Poleg tega - tudi če opisani 3D SoCji po učinkovitosti ne bodo dosegali klasičnih, spajanje računskih in pomnilniških vezij v splošnem mnogo obeta na več področjih. Na primer pri strojnem učenju, kjer se je pokazalo, da tak recept močno zniža porabo čipov za pospeševanje globokih nevronskih mrež, kar zna biti ključno za prihod takšnih procesorjev na rob. Da ne omenjamo sunka, ki ga utegneta doživeti tehnologiji nanocevk in RRAMa.