Slo-Tech - Ranljivost rowhammer, ki so jo raziskovalci na Carneige Mellon University odkrili predlani in za katero je Google praktično izvedbo pokazal lani, napada tudi pomnilniške čipe DDR4 in DDR3 z ECC. Doslej so ti veljali za odporne, a nove raziskave to demantirajo, so povedali na konferenci Semicon China.

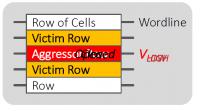

Gre za zanimivo ranljivost, kjer programsko izkoriščamo pomanjkljiv fizični dizajn, ki je posledica miniaturizacije čipov. Ob večkratnem zaporednem dostopu do nekega mesta v pomnilniku (hammering) se namreč z neko verjetnostjo zgodi, da to spremeni bite v sosednjih celicah. To pa ni nujno, da povzroči lahko opazne posledice, kot je zrušitev sistema oziroma ponovni zagon. Kot je pokazal Google lani, je mogoče na ta način z eskalacijo privilegijev pridobiti dostop do računalnika.

Ob razkritju ranljivosti so proizvajalci novih čipov DDR4 zagotavljali, da so ti varni, ker uporabljajo TRR (targeted refresh row) in MAC (maximum access count), ki določata zgornjo mejo števila dostopov do iste pomnilniške celice v časovnem intervalu in osvežujeta sosednje celice. ECC pa tako ali tako uporablja paritetni bit za popravljanje enobitnih napak in zaznavanje dvobitnih.

Preizkus 12 različnih čipov DDR4 je pokazal, da so ranljivi tudi ti čipi. Ne sicer vsi, večina pa. Raziskovalcem je uspelo napad izvesti tudi na procesorskih DDR3 čipih, ki so imeli ECC. V tem primeru so se že v nekaj minutah po začetku napada strežniki sesuli ali ponovno zagnali, pa četudi so nekateri vsebovali posebno zaščito pred rowhammerjem, zaradi katere so povečali frekvenco osveževanja podatkov v pomnilniku.

Novice » Varnost » Tudi DDR4 in DDR3 z ECC ranljiva na obračanje bitov

MrStein ::

ECC pa tako ali tako uporablja paritetni bit za preprečevanje preklopa lihega števila bitov.

Ne, ECC uporablja varianto Hamimmg-a in lahko popravi enobitne napake in zazna dvobitne. Večbitnih napak pa ne zazna.

Motiti se je človeško.

Motiti se pogosto je neumno.

Vztrajati pri zmoti je... oh, pozdravljen!

Motiti se pogosto je neumno.

Vztrajati pri zmoti je... oh, pozdravljen!

McHusch ::

tony1 ::

Torej je problematičen tudi DDR3 brez ECC?

Kje se da dobiti tool s katerim bi se tole stestiralo?

Kje se da dobiti tool s katerim bi se tole stestiralo?

AndrejO ::

Torej je problematičen tudi DDR3 brez ECC?

Kje se da dobiti tool s katerim bi se tole stestiralo?

Kontekst: http://googleprojectzero.blogspot.co.uk...

PoC: https://bugs.chromium.org/p/project-zer...

MrStein ::

ECC pa tako ali tako uporablja paritetni bit

Ne, uporablja dodaten byte (na vsakih 64 bitov podatkov).

Hamming. Ne pariteta.

Motiti se je človeško.

Motiti se pogosto je neumno.

Vztrajati pri zmoti je... oh, pozdravljen!

Motiti se pogosto je neumno.

Vztrajati pri zmoti je... oh, pozdravljen!

sodnicaN ::

>Torej je problematičen tudi DDR3 brez ECC?

ja, že nekaj časa, če imaš 16GB (ena razumna številka za danes) je kar solidna verjetnost da je kateri od bitov pokvarjen

intelova politika da ne dajo ecc podpore v vse čipe pa dela še dodatno škdodo

isti problem je pri trdih diskih in temu da ms še vedno nima nič ekvivalentnega zfsju

>In se da kako zavarovat pred tem ?

še kak več bit namenjen odkrivanju/popravilu pokvarjenih podatkov

ja, že nekaj časa, če imaš 16GB (ena razumna številka za danes) je kar solidna verjetnost da je kateri od bitov pokvarjen

intelova politika da ne dajo ecc podpore v vse čipe pa dela še dodatno škdodo

isti problem je pri trdih diskih in temu da ms še vedno nima nič ekvivalentnega zfsju

>In se da kako zavarovat pred tem ?

še kak več bit namenjen odkrivanju/popravilu pokvarjenih podatkov

win64 ::

sodnicaN ::

ja sej dost protokolov že uporablja podobne fore (recimo za v vsakih 8 bitov podatkov se pošlje 10 bitov)

Ahim ::

sodnicaN ::

ampak to da se pošlje /shrami nekaj dodatnih bitov za namene varovanja podatkov (recimo tudi diski imajo razne error correction code shranjene v ta namen), je pa res, da v primeru pcie zadeva služi še drugim namenom (sinhronizaciji ur, ...)

Vredno ogleda ...

| Tema | Ogledi | Zadnje sporočilo | |

|---|---|---|---|

| Tema | Ogledi | Zadnje sporočilo | |

| » | Napad na pomnilnik Rowhammer omogoča krajo šifrirnih ključevOddelek: Novice / Znanost in tehnologija | 5674 (3917) | MrStein |

| » | Napad rowhammer deluje tudi androidnih telefonihOddelek: Novice / Varnost | 6826 (5013) | srus |

| » | Zloraba spreminjanja bitov v pomnilniku zaradi branja tudi v praksiOddelek: Novice / Varnost | 12068 (10739) | MrStein |

| » | Okvara podatkov v DDR3 zaradi vpliva sosednjih celic (strani: 1 2 )Oddelek: Novice / Pomnilnik | 33456 (29890) | AndrejO |