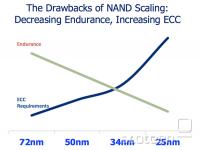

Učinek manjšanja proizvodnega procesa na napake in vzdržljivost

vir: AnandTech

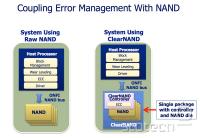

Različni implementaciji ECC-ja - v krmilniku oz. v pomnilniku

vir: AnandTechPrav zato so se pri Micronu odločili, da v same pomnilniške čipe bliskovnega pomnilnika vgradijo preverjanje in popravljanje napak oz. ECC, ki bo deloval neodvisno od krmilnika pomnilniške naprave. To so poimenovali ClearNAND, ki je edinstven za navezo Intel-Micron, glavni konkurent pa je npr. SandForce, ki preverjanje napak vključuje v posledično nekoliko dražji krmilnik. V primerjavi z običajnimi NAND čipi, ki preverjanja ne uporabljajo, bo ClearNAND imel enak razpored pinov, torej bo enostavno uporaben v obstoječih napravah, zasnovanih za 25 nm čipe (za komunikacijo, povezano z ECC; se uporablja prej neizkoriščena povezava VDDI)

ClearNAND čipi bodo prišli v dveh okusih, običajni različici Standard ter zmogljivejši različici Enhanced, ki bo omogočala višje prenose (do 200 MB/s na čip, v primerjavi s 50 MB/s na običajnem), večje število hkratnih dostopov do celic (8 proti 4 na cikel) ter večjo gostoto (16 do 64-gigabajtni čipi v primeru različice Enhanced, le 8 do 32-gigabajtne različice za različico Standard). Osnovna različica bo tako najbolj primerna za pomnilniške kartice, USB ključke, itd., Enhanced pa za SSD pogone, tako za običajne kot za zahtevnejše uporabnike.

Načrti naveze Intel-Micron so sprva sicer napovedovali splavitev 25 nm čipov še pred koncem letošnjega leta, a se kot kaže to ne bo uresničilo, saj bodo eni prvih pogonov s 25 nm pomnilnikom (najverjetneje še brez ECC preverjanja) Intelovi SSD-ji tretje generacije, ki so bili prestavljeni v prvo četrtletje prihodnjega leta. Več pa v izvornem članku.