IBM - Pri IBMu so pompozno predstavili "prvi 2-nanometrski čip na svetu". Po eni strani gre šele za konceptno zasnovo, saj IBM ne razvija končnih izdelkov, obenem pa vezje tudi nima zares 2 nm velikih elementov. Po drugi plati je to bržkone v tem trenutku res vrhunec tehnologije GAAFET/nanosheet in praktične rabe EUV litografije.

Tranzistorji tipa FinFET, ki sestavljajo aktualne procesorje, se približujejo mejam zmogljivosti, zato so izdelovalci ter snovalci računalniških čipov že do vratu v razvoju naslednjih generacij tranzistorjev. Po "tridimenzionalnem" kanalu s pokončno plavutko bodo prihodnji kanali sestavljeni iz nanožičk in nanolističev (nanowire/nanosheet), kar uradno imenujejo GAAFET, za gate-all-around FET. Medtem ko TSMC pri svojem 3 nm procesu še vztraja s FinFET, se je Samsung tu že odločil za GAAFET. Dodatno izpopolnjeno zasnovo so sedaj predstavili pri IBMu, ki sicer večjih proizvodnih kapacitet nima več (leta 2014 jih je prodal GlobalFoundries, zase pa ohranil laboratorijsko proizvodnjo) in ne snuje več končnih izdelkov, zato pa s skorajda vsemi ostalimi velikani plodno sodeluje pri bazičnih raziskavah čipovnih zasnov.

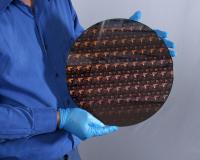

Predstavljeno vezje tako nima imena, temveč ga imenujejo preprosto prvi 2 nm čip na svetu. Takoj je treba poudariti, da taki nazivi že več generacij ne povedo več neposredno velikosti elementov kot nekoč, temveč gre za neke sorte ekvivalent. (Zaradi takšne slabe določenosti so zaznavne razlike tudi med procesi različnih proizvajalcev in ima Intelov 10 nm proces podobno velikost elementov kot TSMC 7 nm.) Če pogledamo shemo natančneje, pri novem IBMovem čipu dolžina vrat znaša 12 nm, širina celice pa 40 nm, pri čemer je razmik med celicami 44 nm. Kanal sestavljajo tri plasti nanolističev, od katerih je vsak debel 5 nm. Če to pretvorimo v rahlo bolj praktično ponazoritev, v podjetju pravijo, da lahko na ta način stlačijo "50 milijard tranzistorjev na površino velikosti nohta". Ker je to sila nedoločljiva metrika, so pri Anandtechu iz njih izvlekli, da z nohtom mislijo 150 kvadratnih milimetrov, kar je dejansko nekaj bolje kot pri TSMC 3 nm procesu.

Poudariti velja, da je za dosežek ključna uporaba EUV litografije na vseh stopnjah procesa, pa še nekaj drugih zanimivosti. Prvenstveno dodatna izolacijska plast pod celotnim kanalom od izvora do ponora (bottom dielectric isolation ali BDI), ki je zaslužna, da elektroni pri teh merah ne bežijo preveč v okolico. Kaj točno sicer stoji na prikazani rezini, niso povedali, verjetno pa je šlo za kombinacijo NAND pomnilniških celic in preprostejše računske logike. Ker je zadeva namenjena v glavnem zbiranju patentov in sodelovanju z dejanskimi proizvajalci ter dizajnerji čipov, je še težko napovedati, kdaj bomo sadove iznajdbe videli v praksi.

Novice » Procesorji » IBM predstavil 2-nanometrski čip

Izi ::

Se pravi so izdelovalci čipov vse bolj podobni izdelovalcem pralnih praškov. Njihovo oglaševanje 10 nm je fizično v resnici 50 nm.

AgiZ ::

Da se grejo razvoj tehnologije samo zaradi patentov brez kake proizvodne uporabe, je tudi malo smešno.

Gregor P ::

Povej to unim, ki plačujejo za patente

The main failure in computers is usually located between keyboard and chair.

You read what you believe and you believe what you read ...

Nisam čit'o, ali osudjujem (nisem bral, a obsojam).

You read what you believe and you believe what you read ...

Nisam čit'o, ali osudjujem (nisem bral, a obsojam).

7982884e ::

Se pravi so izdelovalci čipov vse bolj podobni izdelovalcem pralnih praškov. Njihovo oglaševanje 10 nm je fizično v resnici 50 nm.

am, ne. problem je samo, da oznake niso primerljive med proizvajalci. noben kupec ni zaveden v smislu, da pricakuje 7nm strukture, dobi pa 40nm strukture.

MrStein ::

Da se grejo razvoj tehnologije samo zaradi patentov brez kake proizvodne uporabe, je tudi malo smešno.

Malo smešno, da Petrol prodaja gorivo, ne prodaja pa motorjev, ki bi to gorivo porabili...

Motorje prodaja nekdo drug. Ni problema.

Motiti se je človeško.

Motiti se pogosto je neumno.

Vztrajati pri zmoti je... oh, pozdravljen!

Motiti se pogosto je neumno.

Vztrajati pri zmoti je... oh, pozdravljen!

filip007 ::

Nič se bati, bodo to porabili za Power11 CPU.

Zero games, zero talk.

https://pristytools.neocities.org

https://pristytools.neocities.org

BT52 ::

V končno fazi je vseeno kako kličejo kaj. Na koncu je važen performance in izvedba čipa skupaj z proizvodnim procesom. Recimo znano je, da pri TSMC 7nm je vsaki drugi "heavy compute" transistor izklopljen. Da preprečijo leakeage. Plus te strukture so daleč daleč od minimalne "resolucije" in se gre pri čipu bolj za kompromise, kaj stranka potrebuje.

Vredno ogleda ...

| Tema | Ogledi | Zadnje sporočilo | |

|---|---|---|---|

| Tema | Ogledi | Zadnje sporočilo | |

| » | Proizvodni procesi za čipe v različnih podjetjih (strani: 1 2 3 )Oddelek: Strojna oprema | 17987 (1168) | pegasus |

| » | EU do leta 2030 s proizvodnjo čipov v 5 nm (strani: 1 2 )Oddelek: Novice / Ostale najave | 18343 (14835) | Zimonem |

| » | TSMC že sredi množične 5 nm proizvodnjeOddelek: Novice / Procesorji | 10116 (7992) | FireSnake |

| » | Kitajski SMIC pognal komercialno proizvodnjo čipov FinFETOddelek: Novice / Ostale najave | 5740 (4489) | Mr.B |

| » | IBM izdelal prvi 7-nm čipOddelek: Novice / Procesorji | 12366 (8971) | Qushaak |